# Effect of Bond Layer Properties to Thermo-Mechanical Stresses in Flip Chip Packaging

Y. W. Pok, D. Sujan, M. E. Rahman, S. S. Dol

School of Engineering and Science, Curtin University Sarawak Campus, CDT 250, 98009 Miri, Sarawak, Malaysia

Abstract. The flip chip bonding technology is widely used in electronic packaging as a result of improvements towards mechanical performance of layered structures. However, thermal mismatch shear and peeling stress are often induced by the differences of the material properties and geometries of bond layer during the high temperature change at operating stage. Intrinsically, these thermo-mechanical stresses play a very significant role in the design and reliability of the flip chip package. Therefore, this project aims to develop a methodology to find optimized bonding material thermo-mechanical properties and geometries in relation to the packaging layers in order to eliminate or reduce thermal mismatch stresses that occur in multi-layered structures in electronic packaging. The closed-form solution of thermo-mechanical analysis of bi-material assembly with bond layer is provided. Parametric study will be carried out in order to study the influence of bond layer parameters on interfacial thermal stresses of a flip chip assembly. These parameters include Young modulus, Coefficient of Thermal Expansion (CTE), Poisson's ratio and thickness of the bond layer. It is found that the shearing stresses and peeling stresses decreased considerably at the interface with the increase of bond layer Young Modulus and thickness. On the other side, bond layer CTE and Poisson ratio show almost no significant effect on the interfacial shearing stress and peeling stress along the interface in a bi-material assembly.

# 1 Introduction

As the dramatic increasing demand of microelectronics over the past decade, flip chip microelectronic packages are increasingly being used in microelectronics system applications such as cellular phones, pagers, laptops, Personal Digital Assistants (PDAs), and watches [1-9].

Original flip chip assembly used the ceramic substrate with CTE that matching with silicon die. However, ceramic substrates are expensive as these materials require high temperature processing, and therefore limits the application of flip chip technology in low cost products. On the other hand, organic substrates are cheaper but the high CTE differences between the substrate and silicon die will induce large thermal stress on the laminate layers during operation of the device. This reliability concern has limited the types of applicable substrate for the flip chip assemblies for many years until the bonding layer was introduced [10-11]. Bonding layer compensates for the difference of material properties between silicon die and the substrate.

However, detrimental thermo-mechanical loadings on flip chip reliability are still a major concern due to CTE mismatch of components in the flip chip assembly even with the introduction of bonding layer [12]. During operation, the multi-material laminated assembly undergoes a significant temperature gradient during cooling. This is mainly due to the heat generated by the circuits and the on-and-off nature of the electronic devices. Besides, the interfaces in multilayered assemblies undergo high stress gradients near the free edge, which will initiates the delamination or micro crack at the free edge. There are two types of major stresses acting between the bonding layer and laminate layers in the flip chip assembly, which is shearing stress and peeling stress.

The importance of such failures is felt more acutely as the power requirement of electronic devices increasing rapidly in recent years. In order to minimize the risk of such structural or functional failures, a detailed and critical understanding of the nature of the interfacial stresses within elastic limit under thermal loading is deemed necessary [13].

Due to limitations of experimental modeling and numerical modeling, analytical modeling had been widely applied in determination of interfacial stresses in the materials and the interfaces. The development of bonded interfacial modeling is inspired by the derivations of Chen and Nelson [14]. Many researchers such as Matthys and Mey [15], Mirman [16], Moore and Jarvis [17], and Ru [18] are contributed in this aspect. Suhir et al. [5] proposed a bi-layered interfacial thermal mismatch model by using integro-differential equation. Sujan et al. [13] had developed another simpler solution using a second order differential equation approach compared to Suhir's solution.

Nevertheless, studies conducted on the effect of bond layer on the interfacial stresses are very few [5, 13-18]. The bond layer acts as interfacial shear stress compliance between the two principal layers. Consequently, it will have some influence on the interfacial stresses in a bimaterial assembly. The value of interfacial shear stress compliance for the bond layer at the interface was proposed by Sujan et al. [13] which is given as  $K_0$  as  $h_0/G_0$ . A Gold-Tin solder bond is introduced as the bond layer between silicon and diamond layers and they show that the effect of bond layer on the interfacial shearing stress. It is found that the interfacial shearing stress is decreased considerably at the interface with the increase of bond thickness. Besides, it is observed that the effect of linear temperature gradient may influence interfacial stresses considerably. However, to date limited attempt has been made to study the effect of the thermal mismatching interfacial peeling stress with bond subjected to differentially uniform temperature change.

Therefore, this paper aims to present both the interfacial shearing stress and peeling stress analysis of flip chip packaging with consideration of bond layer. Subsequently a parametric study was conducted to examine the influence of thermo-mechanical properties of bond layer on interfacial thermal mismatch stresses. The properties focused in this research including CTE, Young's modulus, Poisson ratio and thickness.

# 2 Analytical Model

The analytical model used in this project is developed using second order differential equation which does not involved any integro-differential equation .The model is upgraded by Sujan et al. [13] to a generalized form which will account the differential uniform temperatures in the two layers first and later the temperature gradients through the thickness of the layers.

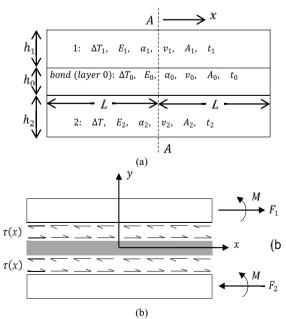

Figure 1. (a) Showing material properties and (b) is the free body diagram of a bi-layered packaging with bond layer at the interface [Adapted from 13].

Figure 1 (a) shows a full length of the model analyzed where A-A represented the center line of the model. The full length of the model is 2L. The model is considered to be a unit of width in a direction perpendicular to the plane of the paper and the forces and moments are defined with respect to the unit width. Figure 1 (b) showed a free body diagram of the model for a cut at some arbitrary x -location with the two layers designated as 1 and 2, and the bond layer as 0.E,  $\alpha$ ,  $\nu$  and h represented elastic modulus, thermal expansion coefficient, Poisson's ratio and thickness of the i-thlayer and is uniform temperature changes in the layers. It is assumed that no external force acting in the layers and axial forces varies along the length, and therefore shear arise at the interface.

For unit width, the force F at any section of layer is given by

$$F_1 = \int_{-L}^{x} \tau dx \tag{1}$$

Here  $\tau$  represents shear stress between the two bonding surfaces per unit depth.

Considering the effect of bond layer effect, the strain compatibility condition relating to the displacements at the two interfaces can be expressed as:

$$\epsilon_{x(1)} - \epsilon_{x(2)} = K_0 \frac{\partial \tau}{\partial x}$$

(2)

Refering to Figure 1 (b), the resultant moment about z-axis at x = 0 and y = 0 is given by,

$$M_1 + M_2 - \frac{1}{2}(h_1 + h_0)F_1$$

$$-\frac{1}{2}(h_2 + h_0)F_2 = 0$$

Substituting  $M_i = \frac{D_i}{R}$  and  $F_1 = F_2 = F$  in eq. (3),

result in

$$\frac{1}{R} = \frac{hF}{2D} \tag{2}$$

Where

$$h = h_1 + h_2 + 2h_0 \tag{3}$$

D is the flexural rigidity given by

$$\sum_{i=1}^{2} D_{i} = \frac{E_{i} h_{i}^{3}}{12(1 - V_{i}^{2})}$$

(4)

The axial strains at the interface of the uniformly heated two layerd structure take the form,

$$\epsilon_{x(1)} = \alpha_1 \Delta T_1 + \lambda_1 F_1 + \frac{h_1}{2R} - K_1 \frac{\partial \tau}{\partial x} \tag{7}$$

$$\epsilon_{x(2)} = \alpha_2 \Delta T_2 - \lambda_2 F_2 - \frac{h_2}{2R} + K_2 \frac{\partial \tau}{\partial x}$$

(8)

Here,

$\alpha_1 \Delta T$ =Strain due to change in Temperature

$\lambda_1 F_1$ =Strain due to thermal mismatch axial force,  $F_1$

$\frac{h_1}{2R}$ =Strain due to bending

$K_1 \frac{\partial \tau}{\partial x}$  = Strain due to shearing force

Where i=1.2

Replacing the components of  $\in_{x(1)}$  and  $\in_{x(2)}$  from eq. (7) and eq.(8), eq. (2) takes the form as,

$$(\alpha_1 \Delta T_1 - \alpha_2 \Delta T_2) + \lambda F$$

$$- (K_1 + K_2) \frac{\partial \tau}{\partial x}$$

$$= K_0 \frac{\partial \tau}{\partial x}$$

(5)

Where

$$\lambda = \lambda_1 + \lambda_2 + \frac{h(h_1 + h_2)}{4D} \tag{6}$$

Differentiating eq. (9), results in a 2<sup>nd</sup> order differential equation as,

$$\frac{\partial^2 \tau}{\partial x^2} - \kappa^2 \tau = 0.,\tag{7}$$

Here

$$\kappa^2 = \frac{\lambda}{K}$$

and  $K = K_1 + K_2 + K_0$

Where

$$K_1 = \frac{h_1}{3G_1}$$

,  $K_2 = \frac{h_2}{3G_2}$ , and  $K_0 = \frac{h_0}{G_0}$

With reference to [13], the solution of eq. (11) can be written as,

$$\tau = C_1 \sinh(\kappa x) C_2 \sinh(\kappa x) \tag{8}$$

Applying boundary conditions at x = 0,  $\tau = 0$  and at x = L,  $F_1 = F_2 = 0$ , Eq. (7) and eq.(8), become

$$K\frac{\delta \tau}{\delta x} = \alpha_1 \Delta T_1 - \alpha_2 \Delta T_2,\tag{9}$$

Applying the boundary conditions, the shear stress  $\tau(x)$  is given by,

$$\tau = \frac{(\alpha_1 \Delta T_1 - \alpha_2 \Delta T_2)}{K\kappa \cosh(\kappa L)} \sinh(\kappa x) \tag{10}$$

The peeling stress expression can be obtained from the consideration of moment equilibrium of the applied forces combined with the shearing stress given by eq. (14). To develop the peeling stress model similar steps given by Sujan et al. [13] can be applied and the expressions for peeling stress can be obtained as follows:

$$P = \frac{(h_1 D_2 - h_2 D_1)}{2D} \frac{(\alpha_1 \Delta T_1 - \alpha_2 \Delta T_2)}{K \cosh(\kappa L)} \cosh(\kappa x)$$

(11)

It is observed that eq. (14) and eq. (15) are of same expressions as equations for the case of bi-material assembly without bond layer effect. The major differences are

$$h = h_1 + h_2 + 2h_0, \lambda_1 + \lambda_2 + \frac{h(h_1 + h_2)}{4D},$$

(12)

and  $K = K_1 + K_2 + K_0$  that the quantities  $h, \lambda$ , and K are all redefined. The quantity  $\kappa$ , although given by the same expression in terms of K and  $\lambda$ , is also redefined.

# 3 Case Study: Silicon-Diamond System

A typical flip chip package, silicon-diamond system was used in this study. **Table 1** below showed the parameters used to calculate the interfacial stresses by using the analytical approach .The length of the assembly is 2L = 0.005m. The temperature change,  $\Delta T$  is taken at  $60^{\circ}$ C in this computation.

Table 1. Material properties and dimension for case study.

|                                     | M <sub>1</sub> (Die) | M <sub>2</sub> (Die attach) | M <sub>0</sub> (Solder) |

|-------------------------------------|----------------------|-----------------------------|-------------------------|

| Young's                             | 188                  | 49.7                        | 7.51-62.5               |

| Modulus, $E_i(GPa)$                 |                      |                             |                         |

| CTE, $\alpha_i(\times 10^{-6}/\ C)$ | 3                    | 25                          | 6.5-28.44               |

| Poisson's ratio , $v_i$             | 0.3                  | 0.29                        | 0.25-0.37               |

| Thickness, $h_i(mm)$                | 0.35                 | 0.15                        | 0.00-0.05               |

## 4 Result and Discussion

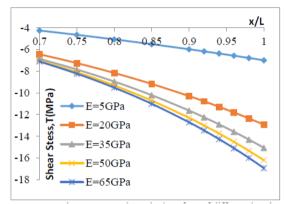

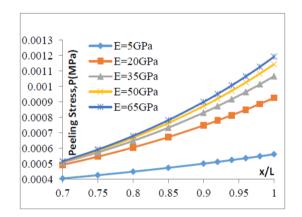

The shearing stress and peeling stress are calculated using eq. (14) and eq. (15) respectively. The results are plotted in Figure 2 to Figure 9. The interfacial stresses are tabulated from x/L = 0.7 to 1, since the stress values and their variations are significantly small when the ratio is lower than 0.7. The maximum shearing stress and peeling stress are recorded at the free end (x/L = 1.0) as expected.

## 4.1 Young's Modulus

Figure 2 and Figure 3 represented shearing and peeling stresses for different values of young modulus along the interface x/L = 0.7 to 1.Here the Young modulus of bond layer,  $E_0$  is varied from 5MPa with increment of 15MPa until 65MPa. From Figure 2 and Figure 3, it can

be observed that the shearing stress is tensile while peeling stress is compressive in nature. The shearing stress and peeling stress decreased due to the compliant (lower young's modulus) bond layer effect at any identical location at the interface. Particularly, near the vicinity of the free end, the differences of thermomechanical stress between highest modulus and lowest modulus of bond layer were significant, which is 76.1% for shearing stress and 84.5% for peeling stress. Thus, it indicated that a more compliant bond will results in smaller interfacial stresses compared to stiffer bond.

**Figure 2**. Shear stresses along the interface of different bond layer Young modulus.

**Figure 3**. Peeling stresses along the interface of different bond layer Young modulus.

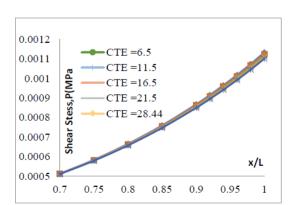

# 4.2 Coefficient of Thermal Expansion

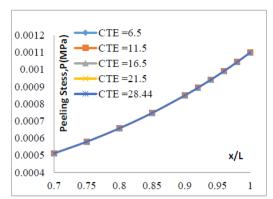

**Figure 4**. Shear stresses along the interface of different bond layer CTE.

**Figure 5**. Peeling stresses along the interface of different bond layer CTE.

Figure 4 and Figure 5 represented shearing stress and peeling stress based on various value of CTE. From Figure , it can observed that shearing stress x/L = 0.7 for  $\alpha_0 = 6.5/^{\circ}\text{C}$  ,the shearing stress reduced by 0.3MPa compared to  $\alpha_0 = 28.44/^{\circ}\text{C}$ . The trends show almost no difference with increment of 5/°C until  $\alpha_0 = 28.44/^{\circ}\text{C}$  towards the end of assembly. On the other side referring to Figure , the peeling stress reduced 12% averagely for  $\alpha_0 = 6.5/^{\circ}\text{C}$   $\alpha_0 = 28.44/^{\circ}\text{C}$  at any identical location along the interface. Therefore, it is evident that the different level of CTE in bond layer have no significant influence in the shearing and peeling stress development.

#### 4.3 Poisson's Ratio

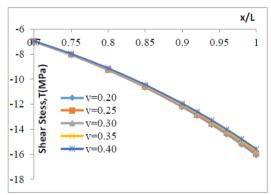

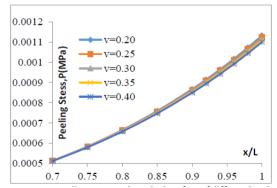

**Figure 6**. Shear stresses along the interface of different bond layer Poisson ratio.

**Figure 7**. Peeling stresses along the interface of different bond layer Poisson ratio.

Referring to Figure 6 and Figure 7, it was demonstrated that Poisson ratio of bond layer do not play significant role in reducing interfacial stresses in flip chip packaging. For higher Poisson ratio and lower Poisson ratio of bond layer, no significant changes of the shearing stress and peeling stress were observed at any identical location. From the above observation it can be concluded that the effect of Poisson ratio in bond layer may not be essential in predicting stresses development at the interface.

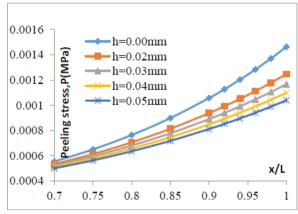

#### 4.4 Thickness

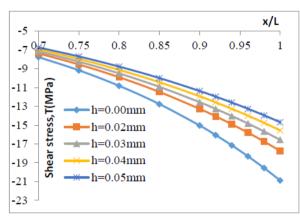

**Figure 8**. Shear stresses along the interface of different bond layer thickness.

**Figure 9**. Peeling stresses along the interface of different bond layer thickness.

Figure 8 and Figure 9 showed the graphical plot of analytical results for shearing stress and peeling stress under different thickness of bond layer. The five different thickness values including negligible bond thickness, 0 mm, and increasing bond thickness of 0.02mm, 0.03mm, 0.004mm and 0.05mm. The thermo-mechanical stresses analysis was presented only for the region near the free end of the assembly since it was the region where the stresses generated significantly.

For both interfacial stresses distribution, the shear stress and peeling stress were observed to be reduced along the length when the thickness of bond layer was being increased. The increased bond layer thickness would generated a surrogate layer acted for shear stress absorption along the interface.

Therefore, a higher value of bond layer thickness would be suggested in the flip-chip packaging design. However, the increased bond thickness was seem to be another concern for the increased overall cost of material.

# 5 Conclusion

The parametric studies on the effect of thermomechanical properties and physical properties of bond layer had been carried out .The results obtained from the analysis leads to following conclusion:

- The shearing stresses and peeling stresses decreased considerably at the interface with the increase of bond layer Young Modulus and thickness.

- Bond layer CTE and Poisson ratio show almost no significant effect on the interfacial shearing stress and peeling stress along the interface in a bi-material assembly.

## References

- 1. Tummala, Rao. Fundamentals of microsystems packaging. McGraw Hill Professional, 2001.

- 2. Moore, Gordon E. "Cramming more components onto integrated circuits."

- Brown, W. D. "Advanced Electronic Packaging with Emphasis on Multichip Modules. ed. WD Brown. 1998."

- 4. Greig, William. Integrated circuit packaging, assembly and interconnections: trends and options. Springer Science & Business Media, 2007.

- Suhir, Ephraim, Yung-Cheng Lee, and C. P. Wong, eds. Micro-and Opto-Electronic Materials and Structures: Physics, Mechanics, Design, Reliability, Packaging: Volume I Materials Physics-Materials Mechanics. Volume II Physical Design-Reliability and Packaging. Vol. 1. Springer Science & Business Media, 2007.

- 6. Vujošević, Milena. "Thermally induced deformations in die-substrate assembly." *Theoretical and Applied Mechanics* 35, no. 1-3 (2008): 305-322.

- 7. Gao, Shubo. "New technologies for lead-free flip chip assembly." PhD diss., Department of Electrical and Electronic Engineering, Imperial College, 2005.

- Chungpaiboonpatana, Surasit, and Frank G. Shi. "Advanced HiCTE flip chip packaging of 90-nm Cu/Low-K chips: Underfill, novel terminal pad structures, and processing optimization." *Journal of electronic materials* 34, no. 7 (2005): 977-993.

- Schubert, A., R. Dudek, H. Walter, E. Jung, A. Gollhardt, B. Michel, and H. Reichl. "Reliability assessment of flip-chip assemblies with lead-free solder joints." In *Electronic Components and Technology Conference*, 2002. Proceedings. 52nd, pp. 1246-1255. IEEE, 2002.

- Wong, C. P., Songhua H. Shi, and G. Jefferson.

"High performance no-flow underfills for low-cost flip-chip applications: material

- characterization." Components, Packaging, and Manufacturing Technology, Part A, IEEE Transactions on 21, no. 3 (1998): 450-458.

- 11. Zhang, Jian. "In-process stress analysis of flip chip assembly and reliability assessment during environmental and power cycling tests." (2003).

- 12. Zhang, Zhuqing. "Study on the curing process of noflow and wafer level underfill for flip-chip applications." (2003).

- 13. Debnath, Sujan, X. Pang, Ekhlasur Rahman, and Mohan Reddy Moola. "Performance study of solder bond on thermal mismatch stresses in electronic packaging assembly." (2012).

- 14. Chen, W. T., and C. W. Nelson. "Thermal stress in bonded joints." *IBM Journal of Research and Development* 23, no. 2 (1979): 179-188.

- 15. Matthys, L. and De Mey, G., 1996. An analysis of an engineering model for the thermal mismatch stresses

- at the interface of a uniformly heated two layer structure. *INTERNATIONAL JOURNAL OF MICROCIRCUITS AND ELECTRONIC PACKAGING*, 19, pp.323-329.

- 16. Mirman, Ilya B. "Effects of peeling stresses in bimaterial assembly." *Journal of Electronic Packaging* 113, no. 4 (1991): 431-433.

- 17. Moore, Thomas D., and John L. Jarvis. "A simple and fundamental design rule for resisting delamination in bimaterial structures." *Microelectronics Reliability* 43, no. 3 (2003): 487-494.

- 18. Ru, C. Q. "Interfacial thermal stresses in bimaterial elastic beams: modified beam models revisited." *Journal of Electronic Packaging* 124, no. 3 (2002): 141-146.